## SONY

# ICX285AL

## 対角11 mm(2/3型)正方画素型白黒用全画素読み出し方式固体撮像素子

#### 概要

ICX285ALは,対角11mm(2/3型)の正方画素配列インタライン型CCD固体撮像素子です。EXview HAD CCD技術の採用により,高感度,低スミアを実現しています。全画素独立読み出し方式により,約1/15秒で全ての画素の信号を独立に出力することが可能です。また,高速ドラフトモードの採用により60 frame/sに対応可能です。電荷蓄積時間の可変な電子シャッタ機能を有し,メカニカルシャッタ無しでフルフレームの静止画を得ることができます。

用途としては,高解像度を必要とするスチルカメラ等の画像入力分野に最適です。

#### 特長

- 全画素独立読み出し

- 高い水平/垂直解像度(共に約1024TV本)の静止画をメカニカル シャッタ無しで実現

- 高速ドラフトモード対応(有効256ライン出力, 60 frame / s)

- 正方画素

- アスペクト比 4:3

- 水平駆動周波数 28.64 MHz

- 高感度,低スミア

- 低暗電流 , 高アンチブルーミング性

- 連続可変速シャッタ機能

- 水平レジスタ 5.0 V駆動

#### 素子構造

- インタライン型CCDイメージセンサ

- イメージサイズ 対角11mm (2/3型)

- 総画素数

有効画素数

実効画素数

1434 (H) × 1050 (V) 約150万画素

1392 (H) × 1040 (V) 約145万画素

実効画素数

1360 (H) × 1024 (V) 約140万画素

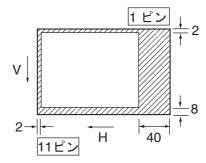

- チップサイズ 10.2mm (H) × 8.3mm (V)

ユニットセルサイズ 6.45 μ m (H) × 6.45 μ m (V)

- オプティカルブラック 水平(H)方向 前2画素 後40画素

- 垂直(V)方向 前8画素 後 2画素

- ダミービット数 水平 20

- 垂直 3

- 基板材質 シリコン

オプティカルブラック配置図 (Top View)

## **EXview HAD CCD®**

\* EXview HAD CCDは、ソニー (株) の登録商標です。

HAD (Hole-Accumulation-Diode) センサを基本構造とし、近赤外光領域まで含め、大幅に光の利用効率を向上したCCDです。

本資料に記載されております規格等は、改良のため予告なく変更することがありますので、ご了承ください。 また本資料によって、記載内容に関する工業所有権の実施許諾や、その他の権利に対する保証を認めたものではありません。な お資料中に、回路例が掲載されている場合、これらは使用上の参考として、代表的な応用例を示したものですので、これら回路の 使用に起因する損害について、当社は一切責任を負いません。

#### 本書に記載された製品のご使用にあたっての注意事項

#### 本製品の用途について

- 本仕様書に掲載された製品(以下,「本製品」といいます。)は,一般電子機器(事務機器,通信機器,計測機器,家電機器など)に使用されることを意図しています。

- 本製品を生命,身体に危害を及ぼす,あるいは重大な物的損害を発生させる虞がある用途の機器にはご使用にならないようお願いします。万一このような用途の機器へのご使用を希望される場合,必ず事前に弊社営業窓口までご相談いただきますようお願い致します。

- また,軍事用途へのご使用はお止めください。

- 本仕様書に掲載された使用条件からの逸脱,本製品を生命,身体に危害を及ぼす,あるいは重大な物的損害を発生させる虞がある用途の機器にご使用になった場合,あるいは本製品の誤った使用,不適切な使用,改造などに起因する損害に関しては,弊社は一切その責任を負いません。

#### 安全設計に関するお願い

• 弊社は本製品の品質並びに信頼性の向上に努めておりますが,万一故障した場合にも,人身事故,火災事故 その他社会的な損害などを生じさせないよう,本製品を用いて製造されたお客様の機器において,冗長設 計,延焼対策設計,誤動作防止設計など安全設計を施されますよう,十分なご配慮をお願いします。

#### 輸出規制

本製品が、「外国為替及び外国貿易法」に定める規制物資に該当する場合、輸出する際には同法に基づく許可が必要になります。

#### 知的財産権等について

本仕様書に掲載した技術資料は、使用上の参考として示したものであり、ご使用に際し弊社及び第三者の 知的財産権その他権利の実施あるいは、使用を許諾したものではありません。依って、その使用に起因する 権利の侵害については、貴社にて解決頂きますようお願い致します。

#### その他

• 本製品のご購入・使用にあたっては,本仕様書の他,弊社の納入仕様書に記載の注意事項等も必ずご参照頂きますようお願い致します。

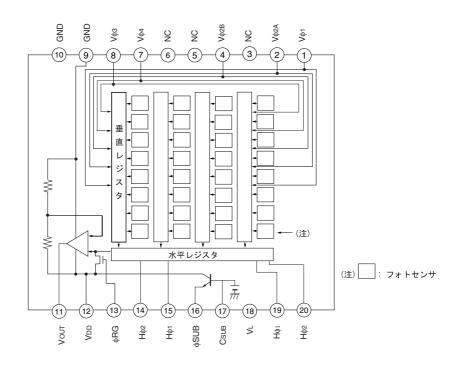

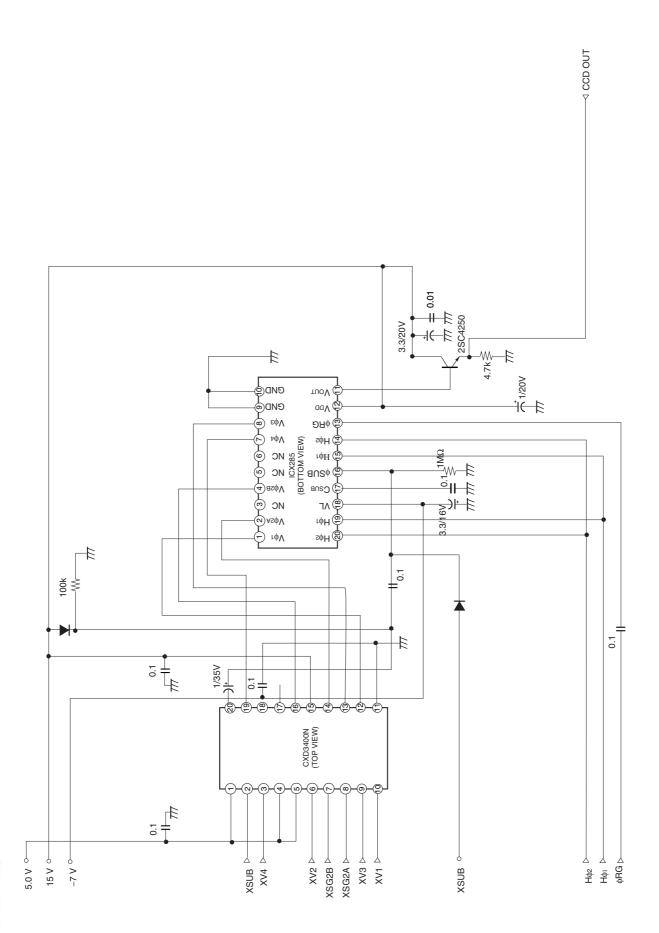

## ブロック図および端子配列図(Top View)

## 端子説明

| 端子番号 | 端子記号 | 端子説明         | 端子番号 | 端子記号            | 端子説明         |

|------|------|--------------|------|-----------------|--------------|

| 1    | V 1  | 垂直レジスタ転送クロック | 11   | Vout            | 信号出力         |

| 2    | V 2A | 垂直レジスタ転送クロック | 12   | V <sub>DD</sub> | 回路電源         |

| 3    | NC   |              | 13   | RG              | リセットゲートクロック  |

| 4    | V 2B | 垂直レジスタ転送クロック | 14   | H 2             | 水平レジスタ転送クロック |

| 5    | NC   |              | 15   | H 1             | 水平レジスタ転送クロック |

| 6    | NC   |              | 16   | SUB             | 基板クロック       |

| 7    | V 4  | 垂直レジスタ転送クロック | 17   | Csub            | 基板バイアス *1    |

| 8    | V 3  | 垂直レジスタ転送クロック | 18   | VL              | 保護トランジスタバイアス |

| 9    | GND  | GND          | 19   | H 1             | 水平レジスタ転送クロック |

| 10   | GND  | GND          | 20   | H 2             | 水平レジスタ転送クロック |

<sup>\*1</sup> CCD内部にてDCバイアスを発生させていますので , 外部に0.1 μ Fの容量を介して接地して下さい。

#### 絶対最大定格

|           | 項目                                | 定格            | 単位 | 備考 |

|-----------|-----------------------------------|---------------|----|----|

|           | Vdd, Vout, RG - SUB               | - 40 ~ + 12   | V  |    |

|           | V 2A, V 2B - SUB                  | - 50 ~ + 15   | V  |    |

| 対 SUB     | V 1, V 3, V 4, VL - SUB           | - 50 ~ + 0.3  | V  |    |

|           | H 1, H 2, GND - SUB               | - 40 ~ + 0.3  | V  |    |

|           | Csub - SUB                        | - 25 ~        | V  |    |

|           | VDD, VOUT, RG, CSUB - GND         | - 0.3 ~ + 22  | V  |    |

| 対GND      | V 1, V 2A, V 2B, V 3, V 4 - GND   | - 10 ~ + 18   | V  |    |

|           | H 1, H 2 - GND                    | - 10 ~ + 6.5  | V  |    |

| 4-4x x    | V 2A, V 2B - VL                   | - 0.3 ~ + 28  | V  |    |

| 対VL       | V 1, V 3, V 4, H 1, H 2, GND - VL | - 0.3 ~ + 15  | V  |    |

|           | 垂直クロック入力端子間電位差                    | ~ + 15        | V  | *1 |

| 入力クロック端子間 | H 1 - H 2                         | - 6.5 ~ + 6.5 | V  |    |

|           | H 1, H 2 - V 4                    | - 10 ~ + 16   | V  |    |

| 保存温度      | - 30 ~ + 80                       |               |    |    |

| 性能保証温度    | - 10 ~ + 60                       |               |    |    |

| 動作温度      |                                   | - 10 ~ + 75   |    |    |

<sup>\*1</sup> クロック幅 < 10  $\mu$  s , クロックDuty Factor < 0.1%の場合には , 24Vまで保証します。電源立ち上げ時 , または電源立ち下げ時には , 16Vまで保証します。

#### バイアス条件

| 項目           | 記号              | 最小値   | 標準値  | 最大値   | 単位 | 備考 |

|--------------|-----------------|-------|------|-------|----|----|

| 回路電源電圧       | V <sub>DD</sub> | 14.55 | 15.0 | 15.45 | V  |    |

| 保護トランジスタバイアス | VL              |       | *2   |       |    |    |

| 基板クロック       | SUB             |       | *3   |       |    |    |

| リセットゲートクロック  | RG              |       | *3   |       |    |    |

<sup>\*2</sup> VL設定は垂直クロック波形のVvL電圧にするか,またはVドライバのVL電源と同じ電圧を使用して下さい。

## 直流特性

| 項目     | 記号  | 最小値 | 標準値 | 最大値 | 単位 | 備考 |

|--------|-----|-----|-----|-----|----|----|

| 回路電源電流 | Idd |     | 9   | 11  | mA |    |

<sup>\*3</sup> 基板クロック端子およびリセットゲートクロック端子にはDCバイアスが内部発生されていますので,DC バイアスを印加しないで下さい。

## クロック電圧条件

| 項目                    | 記号                                 | 最小値    | 標準値   | 最大値   | 単位 | 波形図 | 備考                                     |

|-----------------------|------------------------------------|--------|-------|-------|----|-----|----------------------------------------|

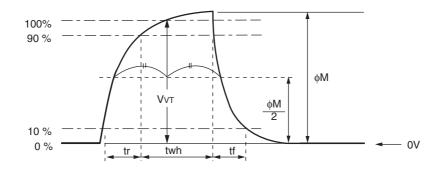

| 読み出しクロック電圧            | VvT                                | 14.55  | 15.0  | 15.45 | V  | 1   |                                        |

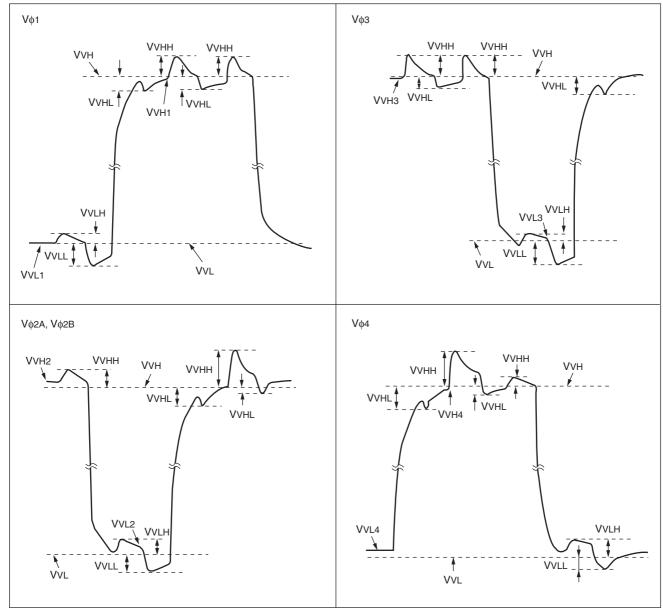

|                       | VVH1, VVH2                         | - 0.05 | 0     | 0.05  | V  | 2   | $V_{VH} = (V_{VH1} + V_{VH2})/2$       |

|                       | VVH3, VVH4                         | - 0.2  | 0     | 0.05  | V  | 2   |                                        |

|                       | VVL1, VVL2,<br>VVL3, VVL4          | - 7.3  | - 7.0 | - 6.7 | V  | 2   | VvL = ( VvL3 + VvL4 )/ 2               |

|                       | V v                                | 6.5    | 7.0   | 7.35  | V  | 2   | V $v = V_{VH} - V_{VL} (n = 1 \sim 4)$ |

| 垂直転送クロック電圧            | Vvh3 - Vvh                         | - 0.25 |       | 0.1   | V  | 2   |                                        |

|                       | V <sub>VH4</sub> - V <sub>VH</sub> | - 0.25 |       | 0.1   | V  | 2   |                                        |

|                       | VVHH                               |        |       | 1.4   | V  | 2   | 高レベルカップリング量                            |

|                       | VVHL                               |        |       | 1.3   | V  | 2   | 高レベルカップリング量                            |

|                       | VVLH                               |        |       | 1.4   | V  | 2   | 低レベルカップリング量                            |

|                       | VVLL                               |        |       | 0.8   | V  | 2   | 低レベルカップリング量                            |

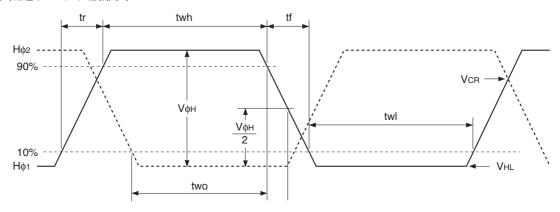

|                       | V н                                | 4.75   | 5.0   | 5.25  | V  | 3   |                                        |

| 水平転送クロック電圧            | VHL                                | - 0.05 | 0     | 0.05  | V  | 3   |                                        |

|                       | Vcr                                | V H/2  |       |       | V  | 3   | クロスポイント電圧                              |

|                       | V RG                               | 3.0    | 3.3   | 5.5   | V  | 4   |                                        |

| │ リセットゲート<br>│ クロック電圧 | Vrglh - Vrgll                      |        |       | 0.4   | V  | 4   | 低レベルカップリング量                            |

| 71774                 | VRGL - VRGLm                       |        |       | 0.5   | V  | 4   | 低レベルカップリング量                            |

| 基板クロック電圧              | V SUB                              | 21.25  | 22.0  | 22.75 | V  | 5   |                                        |

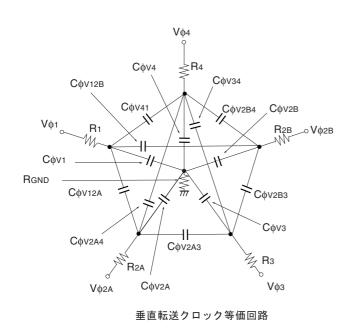

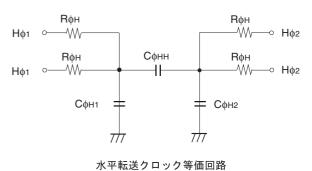

#### クロック等価回路定数

| 項目                   | 記号       | 最小値 | 標準値   | 最大値 | 単位 | 備考 |

|----------------------|----------|-----|-------|-----|----|----|

|                      | C V1     |     | 5600  |     | pF |    |

|                      | C V2A    |     | 6800  |     | pF |    |

| 垂直転送クロック - GND間容量    | C V2B    |     | 22000 |     | pF |    |

|                      | C v3     |     | 8200  |     | pF |    |

|                      | C V4     |     | 22000 |     | pF |    |

|                      | C V12A   |     | 150   |     | pF |    |

|                      | C V12B   |     | 390   |     | pF |    |

|                      | C V2A3   |     | 270   |     | pF |    |

| 垂直転送クロック間容量          | C V2B3   |     | 470   |     | pF |    |

|                      | C V14    |     | 2200  |     | pF |    |

|                      | C V34    |     | 330   |     | pF |    |

|                      | C V2A4   |     | 390   |     | pF |    |

|                      | C V2B4   |     | 560   |     | pF |    |

| 水平転送クロック - GND間容量    | С ні     |     | 47    |     | pF |    |

| が一種区グロググ・GND同合星      | С н2     |     | 39    |     | pF |    |

| 水平転送クロック間容量          | С нн     |     | 74    |     | pF |    |

| リセットゲートクロック - GND間容量 | C RG     |     | 4     |     | pF |    |

| 基板クロック - GND間容量      | C SUB    |     | 1300  |     | pF |    |

|                      | R1, R3   |     | 30    |     |    |    |

| 垂直転送クロック直列抵抗         | R2A, R2B |     | 32    |     |    |    |

|                      | R4       |     | 20    |     |    |    |

| 垂直転送クロック接地抵抗         | RGND     |     | 60    |     |    |    |

| 水平転送クロック直列抵抗         | R н      |     | 7.5   |     |    |    |

| リセットゲートクロック接地抵抗      | R RG     |     | 24    |     |    |    |

R¢rg RG¢ °──₩ C¢rg —

リセットゲートクロック等価回路

#### 駆動クロック波形条件

## (1)読み出しクロック波形図

## (2)垂直転送クロック波形図

$V_{VH} = (V_{VH1} + V_{VH2}) / 2$

$V_{VL} = (V_{VL3} + V_{VL4}) / 2$

$V = V_{VH} - V_{VL} (n = 1 \sim 4)$

#### (3)水平転送クロック波形図

水平転送クロックH 1とH 2の波形のH 1立ち上がり側のクロスポイント電圧をVcrとします。 水平転送クロックH 1とH 2のtwh, twlのオーバラップ期間をtwoとします。

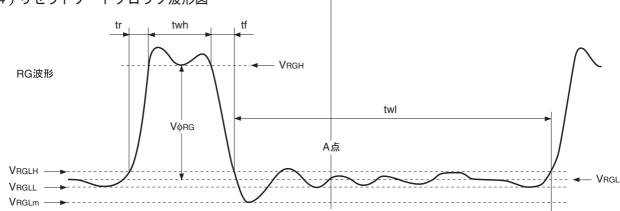

#### (4) リセットゲートクロック波形図

上図A点よりRGの立ち上がるまでの期間のカップリング波形の最大値をVRGLHとし、最小値をVRGLLとします。 また、VRGLHとVRGLLの平均値をVRGLとします。

$V_{RGL} = (V_{RGLH} + V_{RGLL})/2$

twhの期間の最小値をVRGHとし,

$V = RG = V_{RGH} - V_{RGL}$

とします。

RGの立ち下がり時の,負のオーバシュートレベルをVRGLmとします。

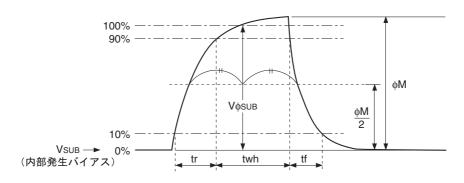

#### (5) 基板クロック波形図

## クロックスイッチング特性 (水平駆動周波数: 28.64 MHz時)

|         | 項目         |     | 記号   |    | twh |      | twl |    |      | tr |    |      | tf  |    | 単    | 備考         |         |             |

|---------|------------|-----|------|----|-----|------|-----|----|------|----|----|------|-----|----|------|------------|---------|-------------|

|         | 4.日        | n 5 |      | 最小 | 標準  | 最大   | 最小  | 標準 | 最大   | 最小 | 標準 | 最大   | 最小  | 標準 | 最大   | 位          | ltti (2 |             |

| 読       | み出しクロック    | VT  |      |    | 2.8 | 3.0  |     |    |      |    |    | 0.5  |     |    | 0.5  |            | μs      | 読み出し時       |

| 垂.      | 直転送クロック    | V   | 1, V | 2, |     |      |     |    |      |    |    |      |     | 15 |      | 250        | ns      | CXD3400N    |

|         | 亜旦料区プロック   |     | 3, V | 4  |     |      |     |    |      |    |    |      |     | 13 |      | <i>230</i> |         | 使用時         |

| 水平      | <br> 映像期間中 | Н   | 1    |    | 10  | 12.5 |     | 10 | 12.5 |    |    | 5    | 7.5 |    | 5    | 7.5        | ns      | tf tr - 2ns |

| 転送      |            | Н   | 2    |    | 10  | 12.5 |     | 10 | 12.5 |    |    | 5    | 7.5 |    | 5    | 7.5        | 113     | u u - 2115  |

| 水平転送クロッ | パラレルシリアル   | Н   | 1    |    |     |      |     |    |      |    |    | 0.01 |     |    | 0.01 |            | μs      |             |

| ク       | 変換時        | Н   | 2    |    |     |      |     |    |      |    |    | 0.01 |     |    | 0.01 |            | μδ      |             |

| IJt     | zットゲートクロック | F   | RG   |    | 4   | 8    |     |    | 24   |    |    | 2    |     |    | 2    |            | ns      |             |

| 基       | <br>阪クロック  | S   | SUB  |    | 3.5 | 3.9  |     |    |      |    |    |      | 0.5 |    |      | 0.5        | μs      | 電荷排出時       |

| 項目       |   | 記号 - |   |   | two<br>標準 | 最大 | 単<br>位 | 備考 |

|----------|---|------|---|---|-----------|----|--------|----|

| 水平転送クロック | Н | 1, H | 2 | 8 | 10        |    | ns     |    |

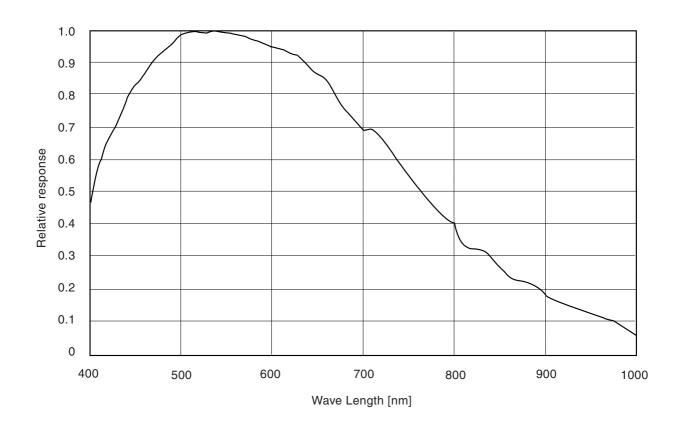

## 分光感度特性例 (ただし,レンズ特性および光源特性を除く)

撮像特性 (Ta = 25 )

| 項目          | 記号   | 最小値  | 標準値   | 最大値   | 単位 | 測定法 | 備考                         |

|-------------|------|------|-------|-------|----|-----|----------------------------|

| 感度1         | S1   | 1040 | 1300  |       | mV | 1   | 1/30秒蓄積                    |

| 感度2         | S2   |      | 4000  |       | mV | 2   | 1/30秒蓄積                    |

| 飽和信号        | Vsat | 850  |       |       | mV | 3   | Ta = 60                    |

| スミア         | Sm   |      | - 110 | - 100 | dB | 4   | 全画素読み出しモード                 |

|             |      |      | - 98  | - 88  | uБ | 4   | 高速ドラフトモード                  |

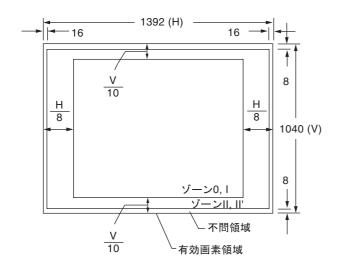

| 映像信号シェーディング | SH   |      |       | 20    | %  | 5   | ゾーン 0, I                   |

|             | 511  |      |       | 25    | 70 |     | ゾーン0~II '                  |

| 暗信号         | Vdt  |      |       | 11    | mV | 6   | Ta = 60 , 15 frame / s     |

| 暗信号シェーディング  | Vdt  |      |       | 4     | mV | 7   | Ta = 60 , 15 frame / s, *1 |

| 残像          | Lag  |      |       | 0.5   | %  | 8   |                            |

<sup>\*1</sup> 垂直レジスタの高速転送による垂直方向の暗信号シェーディングを除く。

## 映像信号シェーディングのゾーン規定

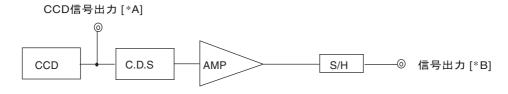

## 測定系

注) AMPの利得は[\*A]~[\*B]間の利得が1となるように調整します。

#### 撮像特性測定法

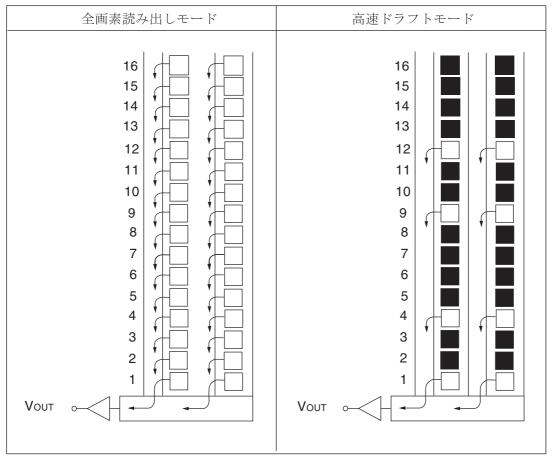

#### 読み出しモード

以下の2つの読み出しモードについて,出力方法を示します。

注) 図中の黒塗り部分は読み出されない画素を示します。 高速ドラフトモードは1ライン目から出力されます。

#### 1. 全画素読み出しモード

1/15秒で全画素の信号をノンインタレースで出力するモードです。

同一露光期間の全画素の信号を同時に読み出すために、高解像度の画像取り込みに適しています。

#### 2. 高速ドラフトモード

8ライン中2ラインの信号 (1ライン目と4ライン目, 9ライン目と12ライン目…) のみを読み出すことで,約1/60秒で全有効エリアを走査します。垂直解像度は約256TV本になります。 垂直解像度より,処理速度を重視した読み出しモードです。

#### 測定条件

- (1)以下の測定において,基板電圧を素子に表示された値に設定し,素子駆動条件は,全画素読み出しモード,バイアス条件,クロック電圧条件標準値とします。

- (2)以下の測定において,点欠陥は除外し,信号出力は特にことわらない限りオプティカルブラック(以下OBと略します)のレベルを基準とし,測定系の[\*B]点で測定した値を用います。

#### 標準撮像状態の定義

- (1) 標準撮像状態I: 輝度706 cd / m², 色温度3200 Kハロゲンランプ使用のパターンボックス(評価用パターンは装着しません)を被写体とします。赤外カットフィルタとしてCM500S (厚さ1.0 mm)を装着した測定標準レンズを使用し, 絞りF8で撮像します。この時の素子受光面への入射光量を標準感度測定光量と定義します。

- (2) 標準撮像状態II: 標準撮像状態Iから赤外カットフィルタを脱着した状態を指します。

- (3) 標準撮像状態III:明るさの均一度が全画角で2%以内の光源(色温度3200 K)を撮像します。赤外カットフィルタとしてCM500S(厚さ1.0 mm)を装着したレンズを使用し,光量はレンズの絞りにより各測定項目に示す光量値に調節します。

- 1. 感度1

標準撮像状態Iに設定し,シャッタスピードを1/100秒とする電子シャッタモードに設定後,画面中央部の信号出力 ( $Vs_1$ )を測定し,次式で算出します。

$$S_1 = V_{S1} \times \frac{100}{30}$$

[mV]

2. 感度2

標準撮像状態IIに設定し、シャッタスピードを1/500秒とする電子シャッタモードに設定後、画面中央部の信号出力( $Vs_2$ )を測定し、次式で算出します。

$$S_2 = V_{S2} \times \frac{500}{30}$$

[mV]

3. 飽和信号

標準撮像状態IIIに設定し, 信号出力平均値を200mVとする光量の20倍に調節後, 信号出力の最小値を測定します。

4. スミア

標準撮像状態IIIに設定し,レンズの絞り値をF5.6~F8の状態で,信号出力平均値を200~mVとする光量の500倍に調節後,読み出しクロックを停止し,各Hブランキングで電子シャッタによる電荷排出を行った時,信号出力の最大値(Vsm[~mV])を測定し,次式で算出します。

$$Sm = 20 \times \log \left( \frac{Vsm}{200} \times \frac{1}{500} \times \frac{1}{10} \right) dB \ ] (1/10V法換算値)$$

5. 映像信号シェーディング

標準撮像状態IIIに設定し,レンズの絞り値をF5.6~F8の状態で,光量を信号出力平均値が200~mVとなるように調節後,信号出力の最大値 (Vmax~[mV~])と最小値 (Vmin~[mV~])を測定し,次式で算出します。

$$SH = (Vmax - Vmin) / 200 \times 100 [\%]$$

#### 6. 暗信号

素子周囲温度を60 で , 素子を遮光状態とし , 水平空送りレベルを基準とした信号出力の平均値Vdt [ mV ]を測定します。

#### 7. 暗信号シェーディング

6に続き , 暗信号出力の最大値(Vdmax [mV])と最小値(Vdmin [mV])を測定し , 次式で算出します。

Vdt = Vdmax - Vdmin [ mV ]

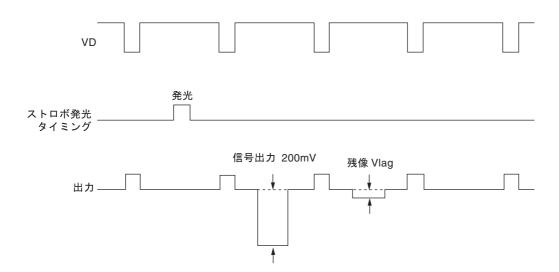

#### 8. 残像

ストロボ光による信号出力を200~mVに調節後 ,ストロボを以下のタイミングで発光させて残信号量 (Vlag)を測定し,次式で算出します。

Lag =  $(Vlag / 200) \times 100 [\%]$

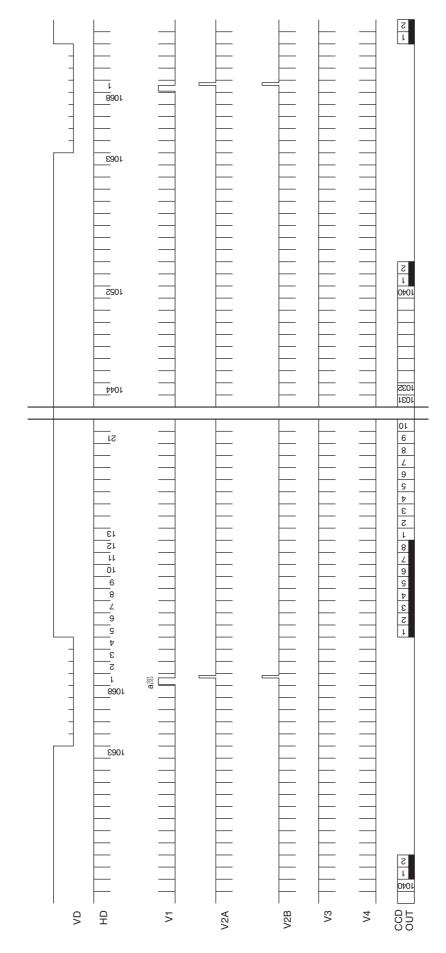

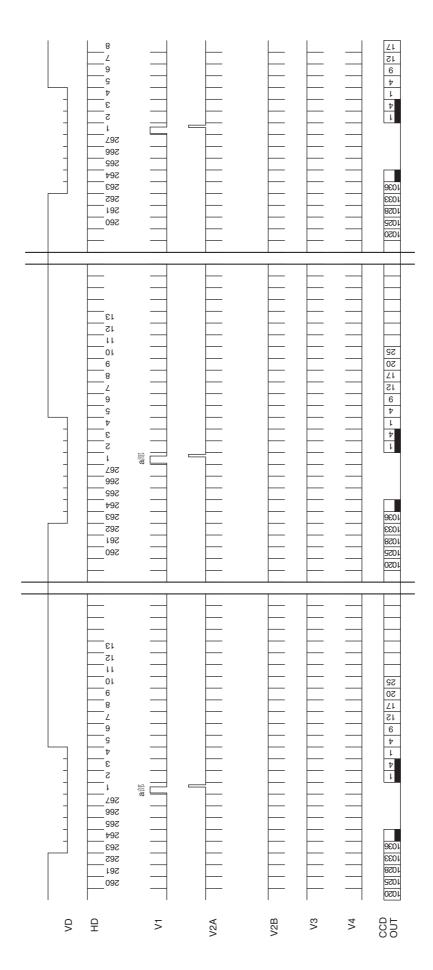

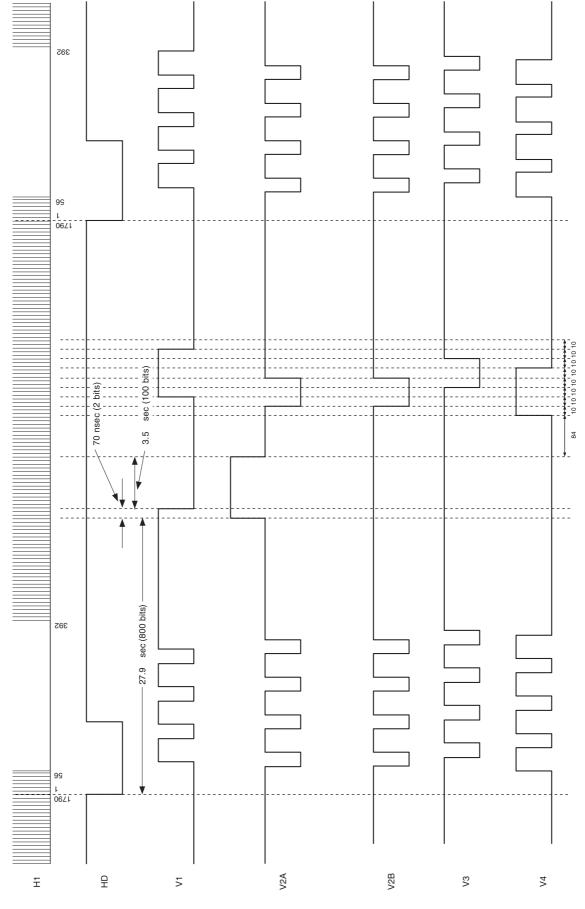

駆動タイミングチャート例(垂直同期)全画素読み出しモード

430

415

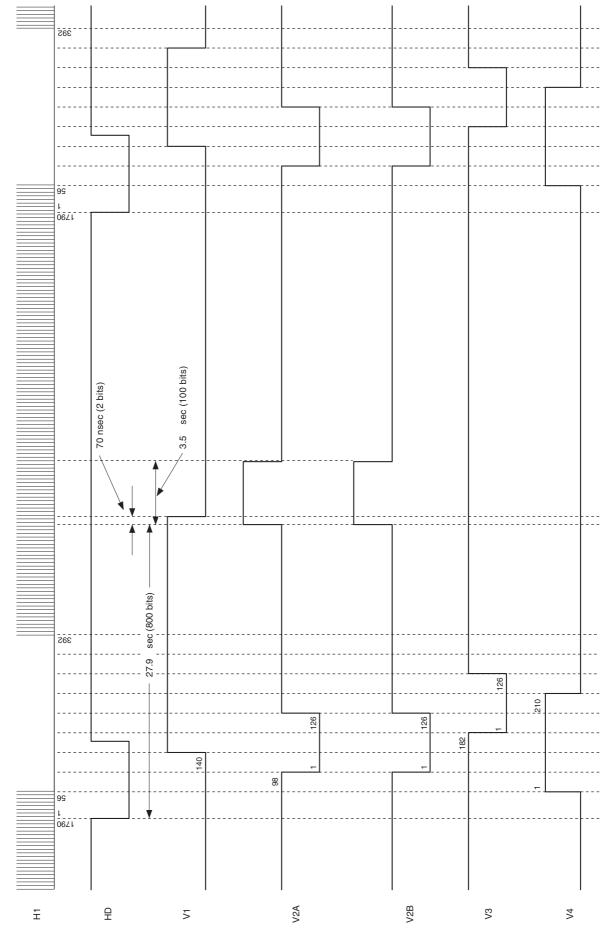

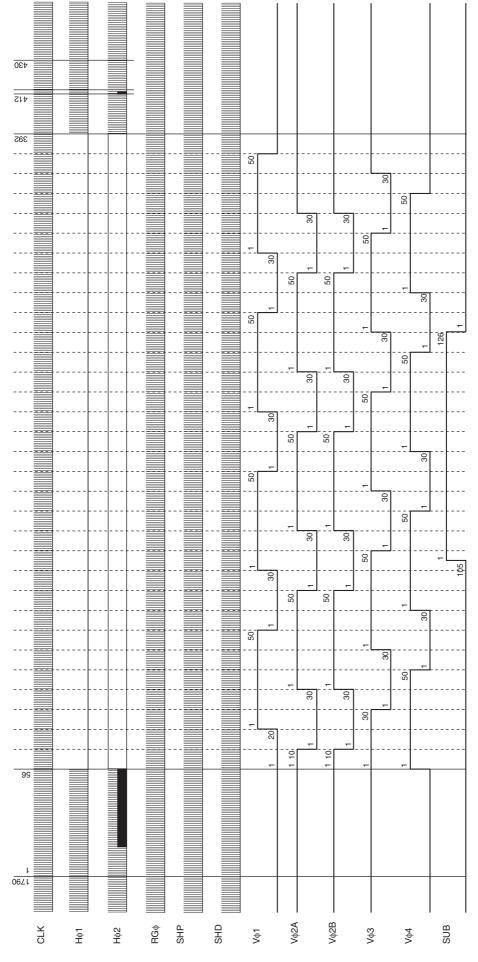

駆動タイミングチャート例(垂直同期 a部拡大)高速ドラフトモード

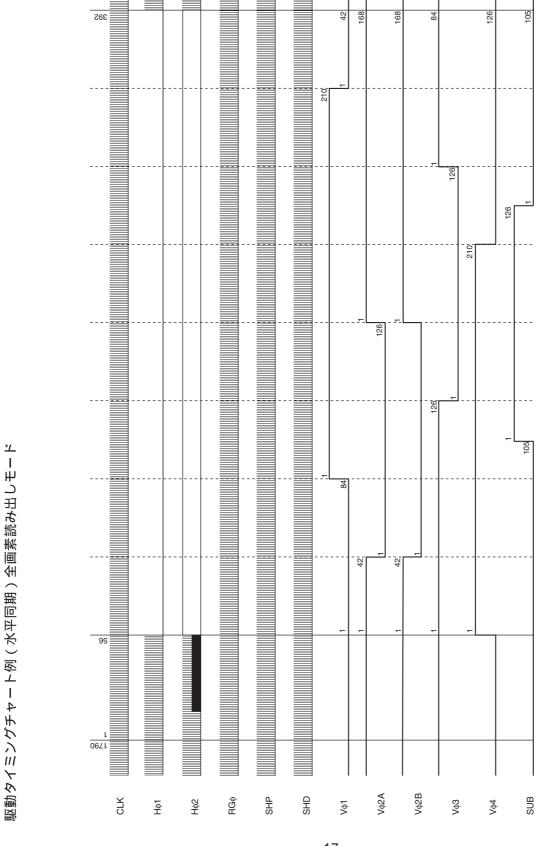

駆動タイミングチャート例(水平同期)高速ドラフトモード

#### 取り扱い上の注意

#### 1) 静電気対策

CCD撮像素子は静電破壊しやすいので、取り扱いに際しては次のような静電気防止対策をお願いします。

- a) 作業は素手または非帯電性の手袋を使用し,作業着なども,非帯電性の物を使用して下さい。 また,靴は導電靴を使用してください。

- b) 直接ハンドリングする場合は, アースバンドを使用して下さい。

- c) 作業場の床 , 作業台などは導電マット等を敷き , 静電気を発生させないようにして下さい。

- d) CCD撮像素子の取り扱いは、イオナイズドエア等で除電することを推奨します。

- e) マウント済の基板を運搬する場合の箱は , 帯電防止処理されたものを使用して下さい。

#### 2) 半田付け

- a) パッケージの温度が80 を超えないようにして下さい。

- b) マウント炉による半田DIPはガラス割れ等の原因になりますので,接地した30Wの半田ゴテで各端子2秒以下で作業して下さい。手直しや取り外し時には十分冷却して下さい。

- c) 撮像素子の取り外しに半田吸引式の器具は使用しないで下さい。電動半田吸い取り器具を使用の際は,温度制御方式がゼロクロスON/OFF型を使用し,接地して下さい。

#### 3) ゴミ・汚れ対策

素子のガラス面は , 使用上有害なゴミ・汚れのないよう , 配慮して梱包納入していますが , 必要に応じて下記のクリーニング作業により清掃除去の上 , 使用してください。

- a) 作業環境は清浄な場所で行ってください。(クラス1000程度が適当です。)

- b) ガラス面には手を触れないように, また, 物を接触させないようにして下さい。 ゴミ等がガラス面に付着した場合は, エアブローで吹き飛ばして下さい。(静電気で付くゴミにはイオ ナイズドエアの使用を推奨します。)

- c) 油脂汚れはエチルアルコールをつけた綿棒等でガラス面にキズを付けないように拭き取って下さい。

- d) ゴミ・汚れ対策として専用のケースに保管し, 結露対策として寒暖の差の激しい部屋の移動には徐熱徐 冷するなどの注意をお願いします。

- e) 出荷時に保護テープが張り付けてある場合は,使用直前に静電気防止対策実施の上剥離して下さい。 なお,保護テープの再使用は行わないで下さい。

- 4) 強い光に長時間さらさないようにして下さい。通常の使用条件を超える過酷な条件での連続使用に際しては,当社にご相談下さい。

- 5) 高温高湿での過酷な条件では特性に影響を与えますので,このような状態での保管および使用は避けて下さい。

- 6) CCD撮像素子は精密光学品のため,過度の機械的衝撃等を加えないようにご注意下さい。

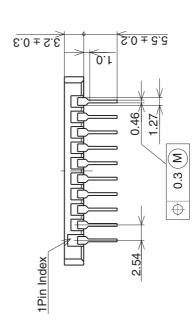

単位: mm

外形寸法図

۵ SE.0S (TAO OPTS TA) .6 of .0 20 pin DIP (800mil) 2.02 ± 0.3 0.5 A  $27.0 \pm 0.3$  $31.0 \pm 0.4$ 20 ပ 0.2 (Reference Hole)  $2-\phi 2.50^{+0.25}_{-0}$ \$2.00<sup>+ 0.15</sup> B

<u>S</u>.0.

0.25

$2.00^{+0.15}_{-0}$  ×2.5 (Elongated Hole)

$26.0 \pm 0.25$

13.15

0.35

1. "A"は有効撮像エリアの中心

垂直方向 (V)の基準は基準穴と長穴の中心を結ぶ直線B

αi

- 水平方向 (H)の基準は基準穴の中心を通り直線Bと直交する直線C 基準穴に対する有効撮像エリアの中心位置: (H, V) = (13.15, 5.0) ±0.15mm 高さ方向の基準はパッケージ底面D (2ヶ所指定) က 4 2

- 直線Bに対する有効撮像面の回転精度:±1° 9

- 底面Dより有効撮像エリアまでの高さ:1.46 ± 0.15mm

- 底面Dに対する有効撮像エリアのアオリ:60pm以下 ω

- シールガラスの厚さは0.75mm(実寸)、屈折率は1.5

PACKAGE STRUCTURE

| Ceramic           | GOLD PLATING   | 42 ALLOY      | 5.90g        | AS-A11(J)      |

|-------------------|----------------|---------------|--------------|----------------|

| PACKAGE MAI ERIAL | LEAD TREATMENT | LEAD MATERIAL | PACKAGE MASS | DRAWING NUMBER |

| בעי         |                  |

|-------------|------------------|

| יטוטטחוט    | MATERIAL         |

| טטחוט שמאטר | DACKAGE MATERIAL |